# DESIGN AND REALISTIC HIGH EFFICIENT ACCURACY CONTROLLABLE ADDER BASED ON SARA KATTA SRI SAI LAKSHMI <sup>1</sup> N.VAMSI KRISHNA<sup>2</sup>

<sup>1</sup> PG. Scholar, Department of ECE, *CHEBROLU ENGINEERING COLLEGE*, Chebrolu, Andhra Pradesh, India.

<sup>2</sup> Assistant Professor, Department of ECE, *CHEBROLU ENGINEERING COLLEGE*, Chebrolu, Andhra Pradesh, India.

# **ABSTRACT:**

Adders and multipliers are the simple units applied in signal preparation. Thus the designation and its engineering typically affect the exhibition of the signal preparing devices. The adders and multipliers are independently streamlined to enhance the presentation of the signal preparing gadgets. In the extra part of the sign handling gadgets, adders are trailed by using multipliers, and henceforth the snake multiplier gadgets are shaped. A method known as 16 bit Adder recoding which converts the contributions to be introduced legitimately to adjust stall shape without consisting of them is talked about within the paper. A snake multiplier unit to enhance its speed has been proposed. Number juggling responsibilities anticipate a widespread element in automated circuit configuration like adders, multipliers, and so forth. Augmentation is a vast essential range-crunching hobby in superior frameworks, for instance, chip and superior signal processors circuits. Usage of multipliers using blower circuit over standard adders will lessen the number of levels of expansion, with the intention to hence decrease the inertness of the multiplier. The multiplier module is probably the fundamental piece of the Multiplier-Accumulator unit plan. Blower primarily based multipliers in MAC engineering configuration results elite. In addition, we propose a postponement versatile self-layout strategy to moreover improve exactness defer Power loss. A new carry-prediction-based accuracy configurable adder design: SARA (Simple Accuracy Reconfigurable Adder). It is a simple design with significantly less area than *CMA*, which, to the best of our knowledge, has not been achieved in the past in accuracy

#### **ISSN : 2057-5688**

configurable adders. SARA inherits the advantages of all previous carry-prediction based approaches: no error correction overhead.

Keywords: SARA, CMA, MAC, carry prediction, significantly, area.

### **1. INTRODUCTION:**

Numerous drastically well-known programs, which consist of photograph processing and additionally acknowledgment, are obviously tolerant of tiny errors. These applications are computationally stressful as well as multiplication is their essential mathematics feature, which creates a possibility to exchange off computational accuracy for decreased strength intake. Approximate computing is an effective mistakesmethod for tolerant applications since it could compromise precision for strength, and it currently performs a essential responsibility in such utility domain names [1]. Different errors-tolerant programs have distinctive accuracy necessities, as do various software tiers in a software. If duplicate accuracy is dealt with, energy will sincerely be thrown away while excessive accuracy is not wanted. This indicates that approximate multipliers

need to be dynamically reconfigurable to in shape the several accuracy requirements of various application stages and also programs.

This project makes a specialty of an approximate multiplier fashion which can control accuracy dynamically. A carry-maskable adder (CMA) is usually recommended that may be dynamically configured to function as a state-of-theart carry propagation adder (CPA), a collection of bit-parallel OR gateways, or a mixture of both. This configurability is thought by way of concealing deliver proliferation: the CPA inside the ultimate diploma of the multiplier is modified by the proposed CMA. An approximate tree compressor is utilized to decrease the accumulation layer deepness of the partial product tree.

An approximate multiplier is made the usage of the encouraged adder and compressor. This multiplier,

Volume XIII, Issue IV, 2021

collectively with a general multiplier and additionally the formerly studied approximate multipliers, come to be completed in Verilog HDL the use of a forty five-nm library to assess the strength consumption, vital course keepup, and also style vicinity. Compared with the usual Wallace tree multiplier, the recommended approximate multiplier reduced electricity utilization by way of amongst forty seven. Three% and 56.2% and the crucial route put off through in among 2 9.Nine% and also 60.Five%, depending on the wished computational precision. In addition, its format place forty four.6% emerge as smaller. Comparisons with the recognized approximate multipliers, none of which have any vibrant reconfigurability, show that the encouraged multiplier provided the very first-rate change-off of energy and hold-up in place of accuracy. All multiplier styles are after that evaluated in a real image processing software program.

A lot of approximate computing research have a look at has been targeting math circuits, which might be

#### **ISSN : 2057-5688**

critical foundation for the majority of In precise, laptop gadget. several approximate adder patterns have sincerely been superior. One such fashion [2] attains 60% strength discount for DCT (Discrete Cosine Transform) calculation without making any form of discernible difference to the photos being processed. In low-cost exercise. precision wishes may range for different programs. The advantage of runtime accuracy adjustment is verified in [3], but their estimation is recognized with the useful resource of voltage overscaling, wherein mistakes especially arise on the timing crucial direction related to the maximum extensive little bits, i.e., errors are usually huge. In [4], a format that considers excellent the preceding okay inputs in location of all enter little bits can approximate the final results with the benefit in 1/2 of the logarithmic maintain-up.

Numerous talented augmentation calculations and device plans are created and delivered inside the writing. Shen and Chen [3] constructed up a 2's complement multipliers the use of Booth

calculation. For electricity lower, this multiplier improved the likelihood of incomplete object getting zero. Hypothetical conditions are determined to illustrate the lower of the changing wearing events in the multiplier. Chen et al. [4] planned a sixteen-piece 2's supplement multiplier. The changing carrying events inside the multiplier are decreased for electricity productivity. Stall calculation is applied for midway decrease. item The pressure dissemination is moreover faded via understanding the multipliers relying on column based definitely and half breed based definitely snake wooden. Wang et al. [5] constructed up a hard and fastexhibit multiplier width for lowelectricity software program. Left-tocalculation is proper applied for incomplete object decrease.

The proposed multiplier has rapid highlights alongside low pressure and vicinity productiveness. Zhijun and Ercegovac [6] added an elite stress effective plan of a direct cluster multiplier. The multiplier is a combination of three approaches. Signal

#### **ISSN : 2057-5688**

circulation enhancement method is carried out for incomplete object decrease. Left-to-right jump and decrease cluster parting strategies are implemented for better execution. To accelerate and reduce the pressure usage of the multiplier the creators Chen and Chu [7] have carried out faux pressure concealment technique (SPST) on the multiplier. The replacing strength within the multiplier is furthermore faded with the aid of planning the control sign maintaining circuit. In the paintings proposed thru Krad and Taie [8], the creators have concept approximately the presentation of a 32-piece multiplier which makes use of carry appearanceearlier snake for fractional item expansion and a 32-piece multiplier which uses swell convey viper for growth. Here, speed is taken into consideration as for an element examination. Regarding door defer the multiplier with supply appearance-earlier snake has outflanked the multiplier with swell deliver viper. In deliver appearance a head snake deliver postponement may be faded however extra than 16-bits

Volume XIII, Issue IV, 2021

circuit will turn out to be more intricate. Equal Prefix Adders (PPA) is considered as likely the fastest viper that were planned and created. Equal Prefix Adders were set up due to the fact the first-class circuits for parallel expansion. These adders which might be likewise referred to as Carry Tree Adders have been located to have higher execution in VLSI plans. Four one-of-a- kind Parallel Prefix Adders particularly Kogge Stone Adder (KSA), Brent Kung Adder (BKA), Han Carlson Adder (HCA) and Hybrid Han Carlson Adder (HHCA). Thus, the essential aim of this work is to enhance the deferral of carry growth snake. The development is completed via fusing HCA (Han- Carlson viper) and KSA (Kogge-Stone snake) within the plan of Ripple Carry Adder and Carry Look in advance Adder.

#### **2. LITERATURE SURVEY:**

S. Cotofana, C. Lageweg, S. Vassiliadis, "Addition related arithmetic operations via controlled transport of charge," *IEEETrans. Computers*, vol. 54, no. 3, pp. 243-256, March 2005.

#### **ISSN : 2057-5688**

This paper investigates the Single Electron Tunneling (SET) technology-based computation of basic addition related arithmetic functions, e.g., addition and multiplication, via a novel computation paradigm, which we refer to as electron counting arithmetic that is based on the controlling transport of discrete quantities of electrons within the SET circuit. First. assuming that the number of controllable electrons within the system is unrestricted, we prove that the addition of two n-bit operands can be computed with a depth-2 network composed out of 3n b 1 circuit elements and that the multiplication of two n-bit operands can be computed with a depth-3 network composed out of 4n 1 circuit elements. Second, assuming that the number of controllable electrons cannot be higher than a given constant r determined by practical limitations, we prove that the addition of two n-bit operands can be computed with a depth- n r b 3 network composed out of 3n b 1 b n r circuit elements.

V. Gupta, D. Mohapatra, A. Raghunathan, K. Roy, "Low-Power Digital Signal Processing Using Approximate Adders", IEEE Trans. on CAD, vol. 32, no. 1, pp. 124-137, jan. 2013

Volume XIII, Issue IV, 2021 December

Low power is an imperative requirement for portable multimedia devices employing various signal processing algorithms and architectures. In multimedia most applications, human beings can gather useful information from slightly erroneous outputs. Therefore, we do not need to produce exactly correct numerical outputs. Previous research in this context exploits error resiliency primarily through voltage over scaling, utilizing algorithmic and architectural techniques to mitigate the resulting errors. In this paper, we propose logic complexity reduction at the transistor level as an alternative approach to take advantage of the relaxation of numerical accuracy. We demonstrate this concept by proposing various imprecise or approximate full adder cells with reduced complexity at the transistor level, and utilize them to design approximate multi-bit adders. In addition to the inherent reduction in switched capacitance, our techniques result significantly shorter critical in paths, enabling voltage scaling. We design for video architectures and image compression algorithms using the proposed approximate arithmetic units and evaluate them to demonstrate the efficacy of our We also derive approach. simple

#### **ISSN : 2057-5688**

mathematical models for error and power consumption of these approximate adders. Furthermore, we demonstrate the utility of these approximate adders in two digital signal processing architectures (discrete cosine transform and finite impulse response filter) with specific quality constraints.

C. Liu, J. Han, and F. Lombardi, "A Low-Power, High-Performance approximate multiplier with configurable partial error recovery," Design, Automation & Test in Europe Conference & Exhibition (DATE), Mar. 2014.

Approximate computing has emerged as a potential solution for the design of energyefficient digital systems. Applications such as multimedia, recognition and data mining are inherently error-tolerant and do not require a perfect accuracy in computation. For these applications, approximate circuits may play an important role as a promising alternative for reducing area, power and delay in digital systems that can tolerate some loss of accuracy, thereby achieving better performance in energy efficiency. As one of the key components in arithmetic circuits, adders have been extensively studied for approximate implementation . New methodologies to model, analyze and

Volume XIII, Issue IV, 2021

evaluate the approximate adders have been discussed in . However, there has been relatively less effort in the design of approximate multipliers. A multiplier usually consists of three stages: partial product generation, partial product accumulation and a carry propagation adder (CPA) at the final stage.

S. Hashemi, R. I. Bahar, and S. Reda, "DRUM: A Dynamic Range Unbiased Multiplier for approximate applications," IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 418- 425, Nov. 2015.

In the recent years, power efficiency has emerged as one of the most critical goals of hardware design. Enormous efforts have already been devoted to improve the power levels consumption in various from algorithmic and software level down to circuit and transistor level. Emerging applications in digital signal processing, computer vision, and machine learning have created new power consumption challenges due to their high computational demands. At the same time, these applications also afford new opportunities for novel low-power implementations. In particular, the common feature of these application domains is an

inherent for limited tolerance and insignificant inaccuracies. This error tolerance arises for multiple reasons, including imperfect perception in human sense, noisy input signal, and redundancy in the input data or the absence of a universal best answer. This inherent error tolerance can be exploited using approximate computing, which effectively allows designers to trade off computational accuracy for savings in power consumption and computational complexity.

#### **3. PROPOSED SYSTEM:**

In advanced VLSI technologies power constraints are a well-known challenge. Low power techniques are already extensively studied. A new direction is approximate computing, where errors are intentionally allowed for power reduction. In audio, video, haptic processing, and machine learning in these applications small errors are

indeed acceptable. Approximate computing research has been concentrated on arithmetic circuits. In computing hardware arithmetic circuits are necessary building

# Volume XIII, Issue IV, 2021 December

#### **ISSN: 2057-5688**

blocks. Several approximate adder designs have been developed [1]-[3]. A few approximate designs have been developed to reduce the overall error by intentionally allowing errors in lower bits with shorter carry chain in addition ACA with operation. starts an approximate adder and it with an error detection and correction circuit. Its approximate adder contains significant redundancy, and the error detection/correction circuit further increases area overhead.

In this paper, we propose a new carry-prediction based accuracy configurable adder design: simple accuracy reconfigurable adder (SARA). It is a simple design with significantly less area than CMA, which, to the best of our knowledge, has not been achieved in the past in ACAs. SARA inherits the advantages of all previous carryprediction-based approaches: no error correction overhead, no data stall, and graceful degradation. allowing Compared to GDA [18], SARA incurs 50% less power-delay product (PDP) and can reach the same peak signal-to-noise

#### **ISSN : 2057-5688**

ratio (PSNR). Moreover. SARA demonstrates remarkably better accuracy-power-delay tradeoff than the latest, and arguably the best, previous work RAP-CLA [19]. A delay-adaptive reconfiguration (DAR) technique is developed to further improve the accuracy power-delay tradeoff. The proposed designs are also validated by multiplication and DCT computation in image processing.

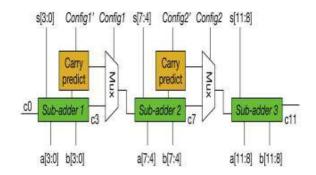

# Fig.3.1.Carry-Prediction-basedconfigurable adder.

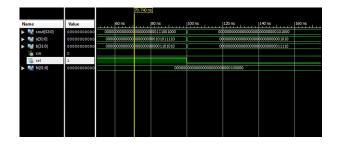

#### **4. RESULTS EXPLANATION**

Although sj+1 is calculated by accurate carry cj , its delay can still be reduced by approximate carry in lower sub-adder. In a multi-bit adder, the delay of sum bit depends on the

Volume XIII, Issue IV, 2021

December

http://ijte.uk/

carry chain propagated from its lower bits. In our SARA structure, even when accurate carry cj is propagated at bit j, the carry chain might be truncated by approximate carry in other lower bits. In Figure 4.3, when c prdt i-1 is propagated, the delay of sj+1 is reduced as its path is shorten to be between bit i - 1 and j + 1. We can take the 12-bit adder in Figure 4.4 as an example. For 12-bit SARA working in approximate mode, the sum s9 uses the accurate carry c8 from a lower sub-adder (bit 5 to 8). But c8 is propagated from approximate carry c prdt 4 of another sub-adder (bit 1 to 4). As shown in the figure, the delay of s9 in SARA is about 6 stages. Compared with the same bit in CRA, the delay of sum bit s9 in SARA is reduced by 3 stages. Similar delay reduction can be observed in other sum bits (bit 6 to 12). For sums at bit 1 to 5, their delay is the same as CRA because they are using an accurate carry c0 from LSB.

#### **ISSN: 2057-5688**

As a result, the maximum delay in 12bit SARA is reduced, since for a multi-bit adder its maximum delay depends on the longest critical path.

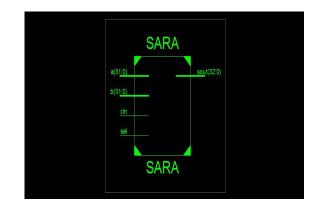

Fig 4.1 RTL schematic of SARA.

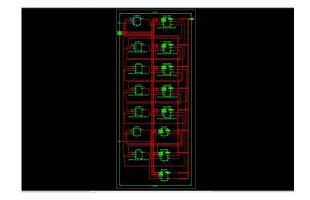

Fig 4.2 Internal schematic of SARA

Volume XIII, Issue IV, 2021

| Device | utilization | summary: |  |  |

|--------|-------------|----------|--|--|

|        |             |          |  |  |

| 49 | out                                 | of                                            | 46560                                                  | 0%                                              |

|----|-------------------------------------|-----------------------------------------------|--------------------------------------------------------|-------------------------------------------------|

| 49 | out                                 | of                                            | 46560                                                  | 0%                                              |

|    |                                     |                                               |                                                        |                                                 |

| 49 |                                     |                                               |                                                        |                                                 |

| 49 | out                                 | of                                            | 49                                                     | 100%                                            |

| 0  | out                                 | of                                            | 49                                                     | 0%                                              |

| 0  | out                                 | of                                            | 49                                                     | 0%                                              |

| 0  |                                     |                                               |                                                        |                                                 |

|    |                                     |                                               |                                                        |                                                 |

| 99 |                                     |                                               |                                                        |                                                 |

| 99 | out                                 | of                                            | 240                                                    | 41%                                             |

|    | 49<br>49<br>49<br>0<br>0<br>0<br>99 | 49 out<br>49<br>49 out<br>0 out<br>0 out<br>0 | <pre>49 out of 49 49 out of 0 out of 0 out of 99</pre> | 49 out of 49<br>0 out of 49<br>0 out of 49<br>0 |

#### Fig.4.4. AREA REPORT

Clock Information:

No clock signals found in this design

Asynchronous Control Signals Information:

No asynchronous control signals found in this design

Timing Summary:

Speed Grade: -2

Minimum period: No path found Minimum input arrival time before clock: No path found Maximum output required time after clock: No path found Maximum combinational path delay: 9.077ns

#### Fig.4.5. TIMING REPORT

#### **Fig.4.6. POWER REPORT**

#### **5. CONCLUSION:**

An accuracy-controllable approximate multiplier has been proposed on this paper that consumes a whole lot less electricity and has a shorter important route postpone than the traditional design. **ISSN: 2057-5688**

Its dynamic controllability is found out by using the proposed CMA. The multiplier modified into evaluated at each the circuit and application degrees. The experimental effects show that the proposed multiplier was able to supply big electricity savings and speedups while maintaining substantially smaller circuit vicinity than that of the traditional Wallace tree multiplier. In addition. SARA has extensive lower region overhead than almost all the preceding works. The accuracy-energypostpone performance is similarly advanced through a put off- adaptive reconfiguration method. We display the efficiency of our adder in the packages of multiplication circuits and DCT computing circuits for picture processing.

#### **REFERENCES:**

[1] S. Venkataramani, V. K. Chippa, S. T. Chakradhar, K. Roy, and A. Raghunathan. "Quality programmable vector processors for approximate computing," 46th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), pp. 1-12, Dec. 2013.

Volume XIII, Issue IV, 2021

December

http://ijte.uk/

[2] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-Inspired imprecise computational blocks for efficient VLSI implementation of Soft-Computing applications," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 4, pp. 850-862, Apr. 2010.

[3] C. Liu, J. Han, and F. Lombardi, "A Low-Power, High-Performance approximate multiplier with configurable partial error recovery," Design, Automation & Test in Europe Conference & Exhibition (DATE), Mar. 2014.

[4] S. Hashemi, R. I. Bahar, and S. Reda, "DRUM: A Dynamic Range Unbiased Multiplier for approximate applications," IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 418-425, Nov. 2015.

[5] B. Moons, M. Verhelst, "DVAS: Dynamic Voltage Accuracy Scaling for increased energy-efficiency in approximate computing," IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), Jul. 2015.

[6] A. Momeni, J. Han, P. Montuschi, and F.Lombardi, "Design and analysis of approximate compressors for

multiplication," IEEE Transactions on Computers, vol. 64, no. 4, pp. 984-994, Apr. 2015.

[7] K. C. Bickerstaff, E. E. Swartzlander, and M. J. Schulte, "Analysis of column compression multipliers," 15th IEEE Symposium on Computer Arithmetic, pp. 33-39, Jun. 2001.

[8] Z. Yang, J. Han, and F. Lombardi,

"Approximate compressors for ErrorResilient multiplier design," IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFTS), pp. 183-186, Oct. 2015.

[9] NanGate, Inc. NanGate FreePDK45

Open Cell Library, http://www.nangate.com/?page\_id=2325,

2008

[10] J. Liang, J. Han, and F. Lombardi, "New metrics for the reliability of approximate and probabilistic adders," IEEE Transactions on computers, vol. 62, no. 9, pp. 1760-1771, Sep. 2013.

[11] M. S. Lau, K. V. Ling, and Y. C. Chu,"Energy-Aware probabilistic multiplier: Design and Analysis," 2009 international Conferrence on Compliers, arc

# Volume XIII, Issue IV, 2021 December h

http://ijte.uk/

#### **ISSN : 2057-5688**

[12] N. Zhu, W. L. Goh, and K. S. Yeo, "An enhanced low-power highspeed adder for error-tolerant application," in Proc. IEEE Int. Symp. Integr. Circuits, Dec. 2009, pp. 69–72.

[13] P. Kulkarni, P. Gupta, and M. D. Ercegovac, "Trading accuracy for power in a multiplier architecture," J. Low Power Electron., vol. 7, no. 4, pp. 490–501, 2011.

**ISSN : 2057-5688**