## ISSN: 2057-5688

# Design & Implementation of Three Operand Adder for Low Power Application.

#### N. SIREESHA, G. NAGA DEEPTHI

PG student, Dept of ECE ,SITS, Kadapa, AP, India

Assistant Professor, Dept of ECE, SITS, Kadapa, AP, India

#### I. ABSTARCT

The most important unit in any electronic device has always been the reasoning and calculation unit. In the new movement, a number shuffling and reasoning unit should have a useful algorithmic action like development and duplication to be significant. Three-operand matched viper is the focal sensible unit to play out the particular ascertaining in different cryptography and pseudorandom bit generator (PRBG) assessments. The most common method for executing the threeoperand extension is the carry save adder (CS3A). Han-Carlson snake (HCA) and the Ladner-Fischer viper (LFA).Two 64-bit hybrid adders were created by selecting the best 32-bit adders and evaluating their performance. Investigations of the viper's exhibition Moreover, the proposed three-operand adder altogether decreases the basic way delay without requiring extra equipment. As a result, a new fast and efficient adder design is proposed that uses a convey prefix calculation-based pre-figure bitwise expansion to carry out the three-operand twofold expansion. This design uses less space, uses less power, and definitely reduces the viper delay. As a result, the three-operand double expansion is presented, which uses less power, uses less space, and definitely reduces the adder delay.

Every two years, more transistors are added to a single integrated circuit (IC) in order to improve performance and speed up VLSI

systems. As the quantity of pieces a framework can deal with increments, postpone increments and execution boundaries like region and power are thus impacted. Improving region, deferral and force of VLSI frameworks have forever been a test. The thing as an originator can do is to achieve any adjustment of the presentation boundaries of any singular part the computerized framework contains with the goal that it can have a general improvement in execution. The digital system's adders, which can be used to perform complex addition, are one such individual component. Increase, deduction and division which should be possible with the assistance of a straightforward adder unit. Mixture adders are blend of at least two adders of same or different sort, a half and half adder can be planned so that the singular viper contained inside the adder defeats the impediment of the other viper utilized, say, a mix of two adders with the end goal that one adder conquers the limit of other adder and end up being profitable in complex calculations. Parallel prefix adders are a type of high-speed adder that can perform addition in parallel (compute the bits simultaneously),

## **II.INTRODUCTION**

Volume XV

Issue IV 2023

December

http://ijte.uk/

making them one of the high-speed adders. Digital systems' operating speeds, frequency of operation, delay, and other performance metrics can be dramatically enhanced by combining these highspeed adders. Exploring mixes of various adders and contrasting their exhibition boundaries is the primary objective of this examination work.

#### **III.LITERATURE SURVEY**

# Design of hybrid (CSA-CSkA) adder for improvement of propagation delay.

Adders are the chief parts in mechanized plans in expansions as well as in channel arranging, multiplexing, and division. The base viper's plan decides the way in which well the circuit works. Utilization of high-performance VLSI (exceptionally large scope reconciliation) frameworks in small and compact devices is growing rapidly. The deferral of the essential snake, which is a crucial boundary for elite execution, determines the rate of activity. To accelerate the viper, various examination projects have been completed to date. A crossover snake circuit with further developed delay is proposed after a similar investigation of different equal adders is directed in this paper. Convey Save Snake (CSA) and Convey Skip Snake (CSkA) have been combined to additionally create inciting delay. The result exhibits the effectiveness of decreasing engendering delay.

Design and execution of 32-bit adders using various full adders.

Computerized signal handling frameworks depend vigorously on adders. The design of 32-bit adders is crucial because many digital systems and processors use 32-bit architecture. In this paper, the arrangement and the execution of various 32-digit adders like

## ISSN: 2057-5688

Wave Convey Snake (RCA), Convey Expansion snake (CINA) and Convey avoid snake (CBYA) for different full snake cells is done using the Verilog HDL. Executing Verilog code in Xilinx 14.5 ISE for the Straightforward 3E family gadget at speed grade -5 yields the results.

### Design of a Scalable Low-Power 1-Bit Hybrid Full Adder for Fast Computation.

A sharp arrangement of a cross variety Full Snake (FA) using Pass Semiconductors (PTs), Transmission Entrances (TGs) and Standard Complementary Metal Oxide Semiconductor (CCMOS) reasoning is presented. The Rhythm toolset was utilized for the circuit's exhibition examination. For the purpose of comparison, twenty additional FA circuits have been compared to the performance parameters. The proposed FA has similarly been loosened up to a word length of 64 parts of test its flexibility. Stretched out to 64 pieces, just the proposed FA and five of the current plans can work without a cradle in the transitional stages. Based on simulation results, the product's low power delay can be attributed to the proposed design's notable power consumption and delay performance. The consequences of the reenactments show that the proposed half breed FA circuit is an engaging choice for planning the information way for contemporary rapid Focal Handling Units.

**High performance Adder Circuit in VLSI system.** This article presents an elite exhibition half breed full snake (HPHFA) planned with static CMOS rationale and pass semiconductor rationale to accomplish better power defer item (PDP). The cadence virtuoso tool was used to implement the circuit on gpdk 45 nm and 90 nm CMOS process technologies. Further, the construction has been

Volume XV Issue IV

V 2023

December

http://ijte.uk/

reached out to 32 pieces to test the exhibition of HPHFA in higher-request hardware. The proposed plan was contrasted and well known regular adders in view of force utilization, delay and PDP. When compared to other conventional full adders (FAs), the proposed adder cell improves speed by 5.08–70.50% and power consumption by 6.31–48.03% in 45 nm. In addition, the improved driving capability and robustness against process variation of the proposed design are features.

## IV.THREE-OPERAND BINARY ADDER TECHNIQUES

In comparison to the three-operand convey save matched viper, the HCA-based three-operand twofold snake (HC3A) significantly reduces the fundamental surrender. Of course, the district loads up regarding bit length in the mentioning O(n log2 n). To decrease this split among region and deferral, a subsequent rapid, area effective three-operand snake strategy and its able VLSI setup are proposed in the accompanying segment.

Issue IV

## ISSN: 2057-5688

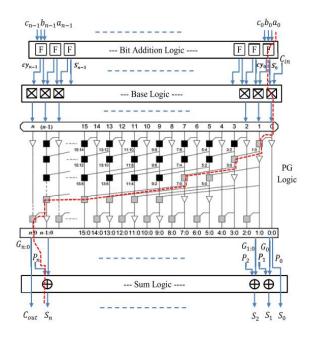

Figure:2 Proposed three-operand adder.

#### Figure:3

3(a) Black cell. 3(b) Gray cell.

3(c) Sum logic.

Another viper strategy and its VLSI engineering are discussed in this section to demonstrate the three-operand expansion through measured number-crunching. An equal prefix viper is the adder plan that has been proposed. Anyway, it has four-stage structures rather three-stage structures in prefix adder to handle the development of three twofold data operands like piece extension reasoning, base reasoning, PG (cause and make) reasoning and total reasoning. The canny enunciation of this large number of four stages are described as follows,

#### Stage-1: Bit Addition Logic:

$$S'_{i} = a_{i} \oplus b_{i} \oplus c_{i},$$

$$cy_{i} = a_{i} \cdot b_{i} + b_{i} \cdot c_{i} + c_{i} \cdot a_{i}$$

Stage-2: Base Logic:

$G_{i:i} = G_i = S'_i \cdot cy_{i-1}, \quad G_{0:0} = G_0 = S'_0 \cdot C_{in}$  $P_{i:i} = P_i = S'_i \oplus cy_{i-1}, \quad P_{0:0} = P_0 = S'_0 \oplus C_{in}$

Stage-3: PG (Generate and Propagate) Logic:

$$Gi: j = Gi:k + Pi:k \cdot Gk - 1: j,$$

$$Pi: j = Pi:k \cdot Pk-1: j$$

Stage-4: Sum Logic:

$$Si = (Pi \bigoplus Gi-1:0), S0 = P0, Cout = Gn:0$$

Volume XV

2023

December

http://ijte.uk/

258

Figure depicts the three-operand paired viper's propo-VLSI engineering and interior construction. The new ad method adds the three n-bit binary inputs in four stages. the essential stage (bit extension reasoning), the bitw development of three n-digit equal data operands performed with the range of full adders, and each full ad processes "total (Si)" and "convey (cyi)" signals highlighted in Figure. Stage-1 characterizes the sensi articulations for processing the aggregate (Si) and conv (cyi) signs, and Fig. portrays the legitimate outline of piece expansion rationale. 3(b).

The "squared saltire-cell" in Figure addresses calculation of Gi and Pi signals, and there are n +1 salti cells in the base rationale stage. In the primary stage, result signal "aggregate (Si)" bit of the current full ad and the result signal "convey" piece of its right-adjoin full viper are used together to process the create (Gi) a proliferate (Pi) signals in the subsequent stage (base log The reasoning diagram of the saltire-cell is shown in Figu and it is recognized by the going with reasona enunciation,

$$G_{i:i} = G_i = S'_i \cdot cy_{i-1};$$

$$P_{i:i} = P_i = S'_i \oplus cy_{i-1}$$

In the proposed snake procedure, the outside convey in signal (Cin) is also considered for three-operand expansi While addressing the G0 (S0 Cin) in the fundamer saltire-cell of the base thinking, this additional convey in signal (Cin) is taken as obligation to the base thinking. 7 convey calculation stage, or "make and duplicate thinkii (PG), joins faint and lessen cell explanations to pre-proc the convey digit. In Figure, the convey produce Gi is tend to by the dependable design of dull and reduce cells: spre among j and Pi: j utilizes the sound verbalization to repor

Gi:  $j = Gi:k + Pi:k \cdot Gk - 1: j$ ,

Volume XV Issue IV

2023

December

## ISSN: 2057-5688

Pi:  $j = Pi:k \cdot Pk-1: j$

## **RTL Schematic Diagrams of Three Operand** Adder for Low Power Application.

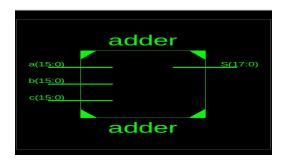

The below figure-1, is the RTL Schematic diagram of Three Operand Adder for Low Power Application. Here a, b, care the inputs of the Three Operand Adder and S is the outputs.

FIG: 1 Schematic Diagrams Three Operand Adder for Low Power Application.

FIG: 2 RTL Internal diagram of Three Operand Adder

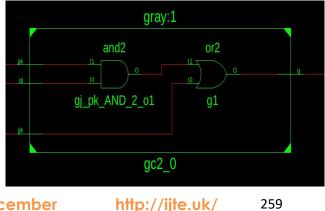

FIG: 3 RTL Internal diagram of Gray Cell.

#

FIG: 4 RTL Internal diagram of Black Cell.

#### **V.SIMULATION RESULT**

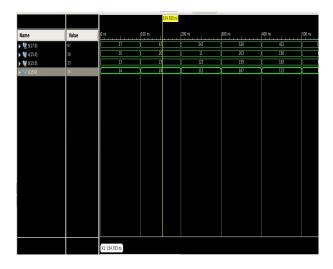

## FIG:5 Simulation result of Three Operand Adder for Low Power Application.

The proposed viper's output waveform is depicted in Fig. 5, where we expanded 16-bit input information for a, b, and c to yield s.

#### CONCLUSION

Three-Operand Twofold Adder for Low Power VLSI Applications is executed in this paper. The presented development of three-operand adder technique is a PPA which can use four-stage ISSN: 2057-5688

structures for calculating the twofold extension of 3-operands. For fair correlation, a similar method of coding is used to plan HC3A and CS3A using the Xilinx 14.7 ISE instrument and Verilog HDL coding. Parallel expansion of 3-operand adders is also introduced. The reduction of region and delay in prefix calculation intentionally works in the piece expansion and PG rationales, which can result in a decrease in ADP and PDP, is the interesting aspect of this newly introduced strategy. Based on the results of the actual combination, it is likely that the display of the introduced viper design expands up to three to multiple times faster than the connected engineering of CS3A, indicating that this adder is superior to other adders in terms of power and delay.

#### REFERENCE

[1] S. Sarkar and J. Mehedi, "Design of hybrid (CSA-CSkA) adder for improvement of propagation delay," 2017 Third International Conference Research in Computational on Intelligence and Communication Networks (ICRCICN), Kolkata, India, 2017, pp. 332-336, doi: 10.1109/ICRCICN.2017.8234530.

[2] S. Janwadkar and S. Das, "Design and Performance Evaluation of Hybrid Full Adder for Extensive PDP Reduction," 2018 3rd International Conference for Convergence in Technology (I2CT), Pune, India, 2018, pp. 1-6, doi: 10.1109/I2CT.2018.8529780.

[3] K. A. K. Maurya, Y. R. Lakshmanna, K. B. Sindhuri and N. U. Kumar, "Design and execution of 32-bit adders using various full adders," 2017 Innovations in Power and Advanced Computing

Volume XV Issue IV

/ 2023

December

nber h

http://ijte.uk/

260

Technologies (i-PACT), Vellore, India, 2017, pp. 1-6, doi: 10.1109/IPACT.2017.8245176.

[4] V. Shah, U. Fatak and J. Makwana, "Design and Performance Analysis of 32-Bit VLSI Hybrid adder," 2019 3rd International Conference on Trends in Electronics and Informatics (ICOEI), Tirunelveli, India, 2019, pp. 1070-1075, doi: 10.1109/ICOEI.2019.8862522.

[5] M. Hasan, M. J. Hossein, M. Hossain, H. U. Zaman and S. Islam, "Design of a Scalable Low-Power 1-Bit Hybrid Full Adder for Fast Computation," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 8, pp. 1464-1468, Aug. 2020, doi: 10.1109/TCSII.2019.2940558.

[6] Arkadiy Morgenshtein, Alexander fish and Israel Wagner "Gate Diffusion input (GDI) – a technique for low power. Design of Digital circuits Analysis and characterization IEEE International symposium on circuit and system February2012.

[7] Sentamilselvi M, Mahendran P "High performance Adder Circuit in VLSI system" International journal of Technology Enhancements and emerging engineering Research IJTEEE VOL 2 Issue3.

[8] Shambhavi Mishra, Gaurav Verma "Low power and Area efficient implementation of BCD Adder of FPGA" IEEE 2013.

[9] Rashmi Chawla, Prashant Kumar, Priya Yadav "Adde Circuit Design using advanced quantum dot cellular Automata (AQCA)" National Conference on Recent Advances in electronics and Computer engineering RAECE 2015.

## ISSN: 2057-5688

[10] Wei wang, Konrad Walus and G.A. Jullien "Quantum Dot Cellular automata adder" IEEE2003.

[11] Mohammad Fawaz, Nader kobrosli, Jessica Rizakallah "Energy minimization feedback loop for ripple carry Adders" 97814244-82740 /10 @ 2010IEEE.

[12] Smita Sharma, Akansha Singh, Krashnkant Gupta "Addition Of redundant binary signed digits using RBSD Adder" 2015 1st International Conference On futuristic trend in Computational analysis and Knowledge management (ABLAZE2015).

[13] Andreas Becher, Jorge Echavarria, Danie Ziener, Stefan Wildermann and Jurgen Teich "A LUT-Based Approximate adder" 2016 24th Annual international Symposium on field Programmable custom Computing Machine.

[14] Alisha, Tilak raj "Tracing of Delay Estimation in Heterogeneous adders with FPGA" IEEE 2017.

Volume XV

Issue IV 2023

December

261